歡迎來深圳市立維創展科技有限公司官方網站!

- 首頁

Home - 關于我們

About Us -

發動機

Engine -

傳感器

Sensor -

集成電路

IC- NXP恩智浦

- ADI wafer Products

- Ampleon

- ARIZONA Capacitors

- Bliley

- Broadcom

- Connor Winfield

- DATEL

- DEI

- DELTA臺達電感

- HOLTIC

- Infineon英飛凌

- iNRCORE

- Interpoint

- Lattice

- Linear Systems

- Marvell

- MaxLinear

- Microsemi

- MTI-MILLIREN

- Princeton Microwave

- Q-TECH

- Renesas瑞薩

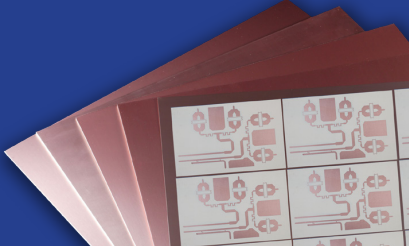

- Rogers

- Solitron DEVICES INC

- STATEK

- VANGUARD ELECTRONICS

- VISHAY

- Wi2Wi(PDI)

- 杰夫微GLF

-

電源模塊

DC-DC -

測試設備

Test -

連接器

Connectors -

產品選型

Select -

行業資訊

Information -

聯系我們

Contact Us